【導讀】本文主要為大家講解的是我們在應用MOS管和設(shè)計MOS管驅(qū)動的時候,寄生參數(shù)是如何影響MOS管的?還有深度剖析下MOS管驅(qū)動電路有哪些要點的?

我們在應用MOS管和設(shè)計MOS管驅(qū)動的時候,有很多寄生參數(shù),其中最影響MOS管開關(guān)性能的是源邊感抗。寄生的源邊感抗主要有兩種來源,第一個就是晶圓DIE和封裝之間的Bonding線的感抗,另外一個就是源邊引腳到地的PCB走線的感抗(地是作為驅(qū)動電路的旁路電容和電源網(wǎng)絡(luò)濾波網(wǎng)的返回路徑)。在某些情況下,加入測量電流的小電阻也可能產(chǎn)生額外的感抗。

我們分析一下源邊感抗帶來的影響:

1.使得MOS管的開啟延遲和關(guān)斷延遲增加

由于存在源邊電感,在開啟和關(guān)段初期,電流的變化被拽了,使得充電和放電的時間變長了。同時源感抗和等效輸入電容之間會發(fā)生諧振(這個諧振是由于驅(qū)動電壓的快速變壓形成的,也是我們在 G端看到震蕩尖峰的原因),我們加入的門電阻Rg和內(nèi)部的柵極電阻Rm都會抑制這個震蕩(震蕩的Q值非常高)。

我們需要加入的優(yōu)化電阻的值可以通過上述的公式選取,如果電阻過大則會引起G端電壓的過沖(優(yōu)點是加快了開啟的過程),電阻過小則會使得開啟過程變得很慢,加大了開啟的時間(雖然G端電壓會被抑制)。

園感抗另外一個影響是阻礙Id的變化,當開啟的時候,初始時di/dt偏大,因此在原感抗上產(chǎn)生了較大壓降,從而使得源點點位抬高,使得Vg電壓大部分加在電感上面,因此使得G點的電壓變化減小,進而形成了一種平衡(負反饋系統(tǒng))。

另外一個重要的寄生參數(shù)是漏極的感抗,主要是有內(nèi)部的封裝電感以及連接的電感所組成。

在開啟狀態(tài)的時候Ld起到了很好的作用(Subber吸收的作用),開啟的時候由于Ld的作用,有效的限制了di/dt/(同時減少了開啟的功耗)。在關(guān)斷的時候,由于Ld的作用,Vds電壓形成明顯的下沖(負壓)并顯著的增加了關(guān)斷時候的功耗。

下面談一下驅(qū)動(直連或耦合的)的一些重要特性和典型環(huán)節(jié):

直連電路最大挑戰(zhàn)是優(yōu)化布局

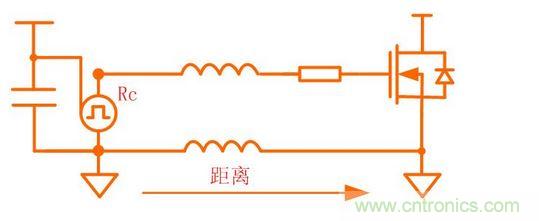

實際上驅(qū)動器和MOS管一般離開很遠,因此在源級到返回路徑的環(huán)路上存在很大的感抗,即使我們考慮使用地平面,那么我們?nèi)耘f需要一段很粗的PCB線連接源級和地平面。

另外一個問題是大部分的集成芯片的輸出電流都比較小,因為由于控制頻率較高,晶圓大小受到限制。同時內(nèi)部功耗很高也導致了IC的成本較高,因此我們需要一些擴展分立的電路。

[page]

旁路電容的大小

由于開啟的瞬間,MOS管需要吸取大量的電流,因此旁路電容需要盡可能的貼近驅(qū)動器電源端。

有兩個電流需要我們?nèi)タ紤]:第一個是驅(qū)動器靜態(tài)電流,它收到輸入狀態(tài)的影響。他可以產(chǎn)生一個和占空比相關(guān)的紋波。

另外一個是G極電流,MOS管開通的時候,充電電流時將旁路電流的能量傳輸至MOS管輸入電容上。其紋波大小可用公式來表明,最后兩個可合在一起。

驅(qū)動器保護

如果驅(qū)動器輸出級為晶體管,那么我們還需要適當?shù)谋Wo來防止反向電流。一般為了成本考慮,我們采用NPN的輸出級電路。NPN管子只能承受單向電流,高邊的管子輸出電流,低邊的管子吸收電流。在開啟和關(guān)閉的時候,無可避免的源感抗和輸入電容之間的振蕩使得電流需要上下兩個方向都有通路,為了提供一條方向通路,低電壓的肖特基二極管可以用來保護驅(qū)動器的輸出級,這里注意這兩個管子并不能保護MOS管的輸入級(離MOS管較遠),因此二極管需要離驅(qū)動器引腳非常近。

晶體管的圖騰柱結(jié)構(gòu)

這是最便宜和有效地驅(qū)動方式,此電路需要盡量考慮MOS管,這樣可以使得開啟時大電流環(huán)路盡可能小,并且此電路需要專門的旁路電容。Rgate是可選的,Rb可以根據(jù)晶體管的放大倍數(shù)來選擇。兩個BE之間的PN結(jié)有效的實現(xiàn)了反壓時候的相互保護,并能有效的把電壓嵌位在VCC+Vbe,GND-Vbe之間。

加速器件

MOS管開通的時候,開啟的速度主要取決于二極管的反向特性。

因此MOS管關(guān)斷的時間需要我們?nèi)?yōu)化,放電曲線取決于Rgate,Rgate越小則關(guān)斷越快。下面有好幾個方案:

[page]

1.二極管關(guān)斷電路

這是最簡單的加速電路。Rgate調(diào)整著MOS管的開啟速度,當關(guān)斷的時候,由二極管短路電阻,此時G極電流最小為:Imin=Vf / Rgate 。

此電路的優(yōu)點是大大加速了關(guān)斷的速度,但是它僅在電壓高的時候工作,且電流仍舊流向驅(qū)動器。

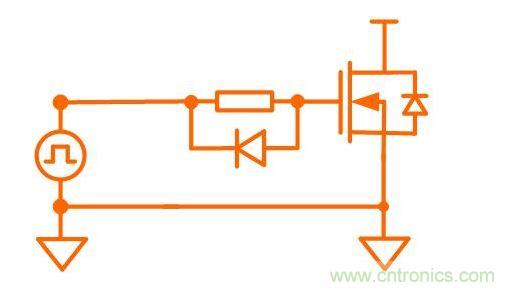

2.PNP關(guān)斷電路

這是最流行和通用的電路,利用PNP的管子,在關(guān)斷期間,源極和柵極被短路了。二極管提供了開啟時候的電流通路(并且有保護PNP管子eb免受反向電壓的影響),Rgate限制了開啟的速度。

電路的最大的好處是放電電流的尖峰被限制在最小的環(huán)路中,電流并不返回至驅(qū)動器,因此也不會造成地彈的現(xiàn)象,驅(qū)動器的功率也小了一半,三極管的存在減小了回路電感。

仔細看這個電路其實是圖騰柱結(jié)構(gòu)的簡化,電路的唯一的缺點是柵極電壓并不釋放到0V,而是存在EC極的壓差。

[page]

3.NPN關(guān)斷電路

優(yōu)點和上面的PNP管子相同,缺點是加入了一個反向器,加入反向器勢必會造成延遲。

4.NMOS關(guān)斷電路

這個電路可以使得MOS管關(guān)斷非常快,并且柵極電壓完全釋放至零電壓。不過小NMOS管子需要一個方向電壓來驅(qū)動。 問題也存在,NMOS的Coss電容和主MOS管的CISS合成變成等效的電容了。