【導(dǎo)讀】隨著轉(zhuǎn)換器帶寬的增加,需在FPGA或ASIC中處理的數(shù)據(jù)量也變得非常龐大。必須找到一種有效的方法,處理來自轉(zhuǎn)換器的那么多數(shù)據(jù)。交錯式ADC無疑是推動接口實(shí)現(xiàn)更高效率的因素之一,能為系統(tǒng)設(shè)計(jì)人員提供多種優(yōu)勢。本文就為大家講講什么是交錯式ADC?

在目前很多細(xì)分市場上,除了JESD204B標(biāo)準(zhǔn)定義外,還需多少額外帶寬?對于這個問題,更為復(fù)雜的答案始終圍繞著交錯式ADC展開。若ADC為交錯式,則兩個或兩個以上具有定義時(shí)鐘關(guān)系的ADC用來同步采樣輸入信號,并產(chǎn)生組合輸出信號,使得采樣帶寬為單個ADC帶寬的數(shù)倍。

交錯式ADC無疑是推動接口實(shí)現(xiàn)更高效率的因素之一,能為系統(tǒng)設(shè)計(jì)人員提供多種優(yōu)勢。然而,隨著轉(zhuǎn)換器帶寬的增加,需在FPGA或ASIC中處理的數(shù)據(jù)量也變得非常龐大。必須找到一種有效的方法,處理來自轉(zhuǎn)換器的那么多數(shù)據(jù)。若采樣速率達(dá)到千兆樣本級別,那么在轉(zhuǎn)換器中繼續(xù)使用LVDS接口將是非常不實(shí)際的。因此,JESD204B是將大量數(shù)據(jù)從轉(zhuǎn)換器傳輸至FPGA或ASIC的有效途徑。

交錯式ADC具有十分廣闊的應(yīng)用空間。在通信基礎(chǔ)設(shè)施中,存在著一種推動因素,使ADC的采樣速率不斷提高,以便在諸如DPD(數(shù)字預(yù)失真)等線性化技術(shù)中支持多頻段、多載波無線電,同時(shí)滿足更寬的帶寬要求。 在軍事和航空航天領(lǐng)域,采樣速率更高的ADC可讓多功能系統(tǒng)用于通信、電子監(jiān)控和雷達(dá)等多種應(yīng)用中。工業(yè)儀器儀表應(yīng)用中始終需求采樣速率更高的ADC,以便精確測量速度更高的信號。

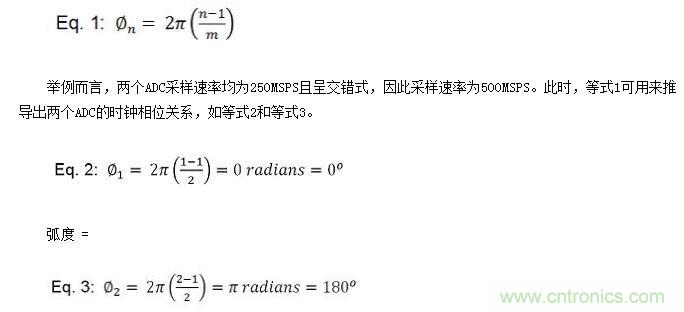

首先,工程師需要對交錯式ADC有一定的了解。利用m個ADC可讓有效采樣速率增加m倍。為簡便起見并易于理解,在本文中重點(diǎn)考察兩個ADC的情況。這種情況下,如果兩個ADC的每一個采樣速率均為fS且呈交錯式,則最終采樣速率為2fS。這兩個ADC必須具有時(shí)鐘相位關(guān)系,才能正確交錯。時(shí)鐘相位關(guān)系由等式1給出,其中:n是某個特定的ADC,m是ADC總數(shù)。

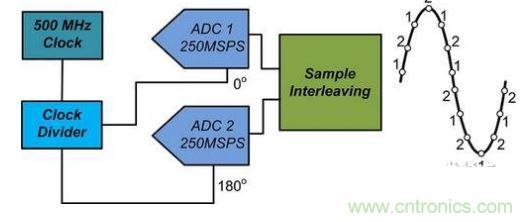

注意,如果已知時(shí)鐘相位關(guān)系,便可檢查樣本結(jié)構(gòu)。圖1以圖形說明時(shí)鐘相位關(guān)系,以及兩個250MSPS交錯式ADC的樣本結(jié)構(gòu)。

圖1 兩個交錯式250MSPS ADC – 基本原理圖

注意180°時(shí)鐘相位關(guān)系,以及樣本是如何交錯的。輸入波形也可由兩個ADC進(jìn)行采樣。此時(shí),采用經(jīng)過2分頻的500MHz時(shí)鐘輸入,便可實(shí)現(xiàn)交錯。分頻器負(fù)責(zé)將所需的時(shí)鐘相位發(fā)送至每一個ADC。

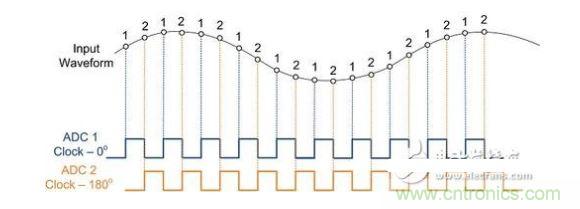

此概念還可以另一種方式表達(dá),如圖2所示。

圖2 兩個交錯式ADC – 時(shí)鐘與采樣

通過將這兩個250MSPS ADC以交錯方式組合,采樣速率便能增加至500MSPS。這樣可以使轉(zhuǎn)換器的奈奎斯特區(qū)從125MHz擴(kuò)展到250MHz,從而工作時(shí)的可用帶寬倍增。工作帶寬的增加可以帶來很多好處。無線電系統(tǒng)可以增加其支持的頻段數(shù);雷達(dá)系統(tǒng)可以增加空間分辨率;而測量設(shè)備可以具有更高的模擬輸入帶寬。

相關(guān)閱讀: