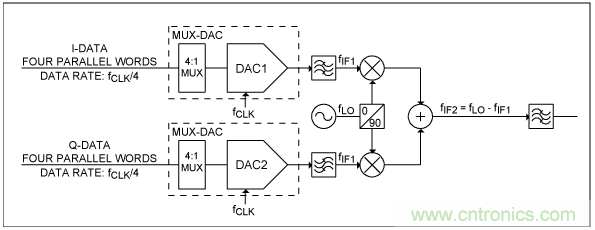

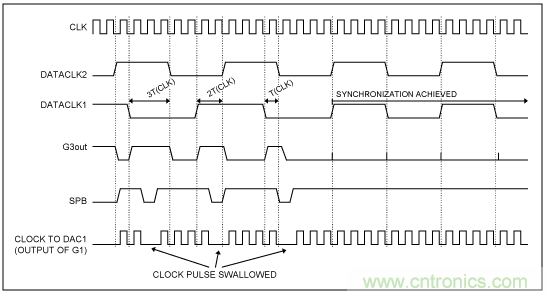

【導讀】在很多發(fā)射應用中必須產(chǎn)生多路相對相位準確已知的模擬輸出。在正交調(diào)制器中(圖 1),I 和 Q 通道必須具有明確的相位關系來實現(xiàn)鏡頻抑制。圖 1 中,DAC1 和 DAC2 的延遲必須匹配。使用數(shù)字波束成形技術的發(fā)射器需要準確地控制大量 DAC 之間的相對相位。

概述

在很多發(fā)射應用中必須產(chǎn)生多路相對相位準確已知的模擬輸出。在正交調(diào)制器中(圖 1),I 和 Q 通道必須具有明確的相位關系來實現(xiàn)鏡頻抑制。圖 1 中,DAC1 和 DAC2 的延遲必須匹配。使用數(shù)字波束成形技術的發(fā)射器需要準確地控制大量 DAC 之間的相對相位。

圖 1. 使用多路復用 DAC 的 I/Q 發(fā)射器中的 DAC 和第一上變頻級

使用具有多路輸入的 DAC (MUX-DAC)如 MAX19692,或具有數(shù)據(jù)時鐘輸出的內(nèi)插 DAC 時,輸入數(shù)據(jù)速率為 DAC 刷新速率的 1/N,DAC 在一個或兩個數(shù)據(jù)時鐘跳變沿鎖存數(shù)據(jù)。MAX19692 中 N = 4,輸入數(shù)據(jù)速率為 DAC 刷新速率的 1/4。DAC 輸出一個由輸入時鐘經(jīng)數(shù)字分頻得到的數(shù)據(jù)時鐘(DATACLK)。DAC 上電時,數(shù)字時鐘分頻器可在 N 個狀態(tài)的任意一個啟動。如果使用多個 DAC,不同 DAC 的時鐘分頻器會在不同的狀態(tài)啟動,所以 DAC 會在不同的時間鎖存數(shù)據(jù)。除非這種情況被發(fā)現(xiàn)并校正,否則不同的 DAC 輸出數(shù)據(jù)時相互之間可能會有一個或更多個時鐘周期的延遲。如果每個 DAC 的時鐘分頻器可以復位,那么這種情況可以避免,但是仍然會存在一些問題。如果其中一個時鐘分頻器發(fā)生錯誤,DAC 會變得永久異相,除非執(zhí)行一些錯誤狀態(tài)檢測方法。為了保證系統(tǒng)的可靠性,必須檢測相位錯誤狀態(tài)并改正。如果 DAC 工作于非常高速的狀態(tài)下,那么復位信號與輸入時鐘的同步也可能是個難題。

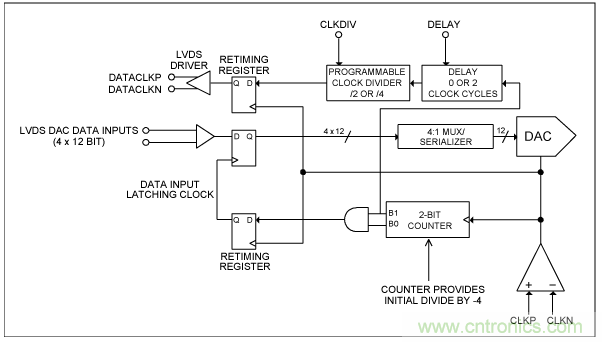

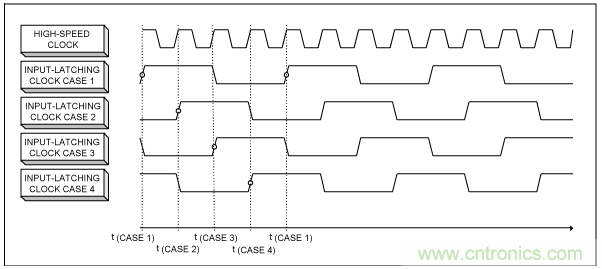

圖 2 所示是 MAX19692 的時鐘(CLKP,CLKN)和數(shù)據(jù)時鐘(DATACLKP,DATACLKN)接口的簡化框圖。初始時鐘由一個兩位計數(shù)器四分頻后用于鎖存數(shù)字 DAC 輸入。該計數(shù)器可能在四個狀態(tài)中的任意一個啟動(圖 3)。如果使用兩個多路復用 DAC,這兩個 DAC 可能會在不同的狀態(tài)啟動。這可能導致 DAC1 的鎖存與 DAC2 的鎖存之間存在 -1、0、1 或 2 個時鐘周期的延遲。

MAX19692 的數(shù)據(jù)時鐘輸出再由數(shù)據(jù)輸入鎖存時鐘進行 2 分頻或 4 分頻。然后數(shù)據(jù)在雙倍數(shù)據(jù)率(DDR)模式下在時鐘的兩個跳變沿進行鎖存,或者在四倍數(shù)據(jù)率(QDR)模式下在時鐘的每 90°相位處進行鎖存。如果多個 DAC 的數(shù)據(jù)時鐘延遲相匹配,或數(shù)據(jù)時鐘相互之間反相,那么鎖存時鐘相匹配。

圖 2. MAX19692 內(nèi)部時鐘接口框圖

圖 3. MAX19692 鎖存時鐘(四種可能的狀態(tài))

DAC 的同步問題有兩個方面:

DAC 的鎖存時鐘之間的相對相位必須被檢測。

DAC 之間的相對相位必須被調(diào)整直到 DAC 被合適地定相。

檢測 DAC 之間的相位誤差可以通過檢測兩個 DAC 之間的數(shù)據(jù)時鐘輸出的相位誤差來實現(xiàn)。相位檢測器可以像一個異或門一樣簡單,也可以像相頻檢測器一樣復雜。

可以通過操作一個或更多個 DAC 的時鐘來實現(xiàn)兩個 DAC 之間的相位調(diào)整,直到 DAC 數(shù)據(jù)時鐘輸出的相對相位為零。另外一種方法可以測量數(shù)據(jù)時鐘之間的 DAC 延遲周期數(shù)和相應的延遲數(shù)據(jù)。下面的段落講述了 I/Q 配置中的這兩種方法。

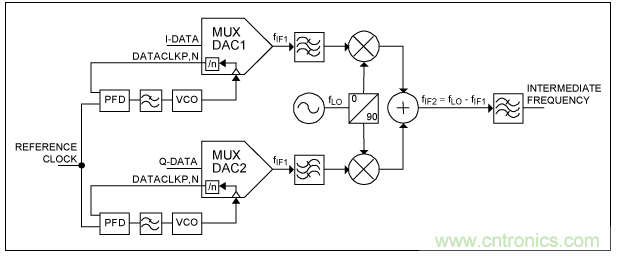

通過“吞”脈沖實現(xiàn) DAC 相位調(diào)整

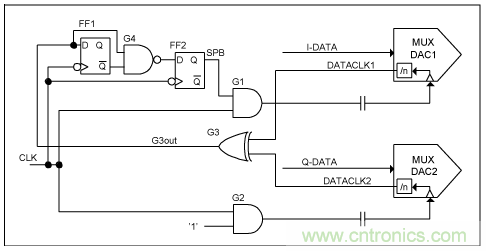

如果 DAC 使用方波(比如 ECL)時鐘,兩個 DAC 之間的同步可以用圖 4 所示的簡單的高速邏輯電路來實現(xiàn)。為了簡單明了,該原理圖中的邏輯配置只能實現(xiàn)單端功能。但是實際應用中會使用差分邏輯如 ECL 來實現(xiàn)高速和低噪聲性能。

圖 4. 實現(xiàn) DAC 同步的簡單的高速邏輯電路

MUX-DAC1 時鐘路徑上與門(G1)的插入允許對 MUX-DAC1 的時鐘進行操作。MUX-DAC2 的時鐘路徑上插入與門(G2)用于延遲匹配。異或門(G3)起相位檢測的作用。當 DATACLK1 和 DATACLK2 的輸出不同時 G3 輸出“1”。如果 G3out = “1”,應該“吞掉” MUX-DAC1 的時鐘脈沖,將 DATACLK1 的邊沿移位一個 CLK 時鐘周期。G3 輸出的上升沿(G3out)由 FF1 和 G4 組成的上升沿檢測器(PED)來檢測。如果檢測到上升沿,PED 輸出“0”,持續(xù)一個時鐘周期。在 SPB 應用于 G1 之前,F(xiàn)F2 將這個信號重新定時,從而使 MUX-DAC1 的一個時鐘脈沖被抑制。這就使 DATACLK1 延遲一個 CLK 時鐘周期。經(jīng)過若干個時鐘周期后,DATACLK1 的延遲與 DATACLK2 一致,如圖 5 所示。使用這種方法時,觸發(fā)器要在時鐘的下降沿進行狀態(tài)更新,以消除 DAC 時鐘信號的毛刺,兩個 MUX-DAC 的輸入時序要相同。布線時要考慮延遲以確保滿足兩個觸發(fā)器的建立和保持時間的要求,且在時鐘為低時將 SPB 信號的脈沖應用于 G1。否則,時鐘信號可能會產(chǎn)生毛刺。同時建議使用無噪聲電源為時鐘同步電路供電,將抖動的引入減到最小。

圖 5. 所示邏輯電路操作的時序圖

通過輸入數(shù)據(jù)移位實現(xiàn) DAC 相位調(diào)整

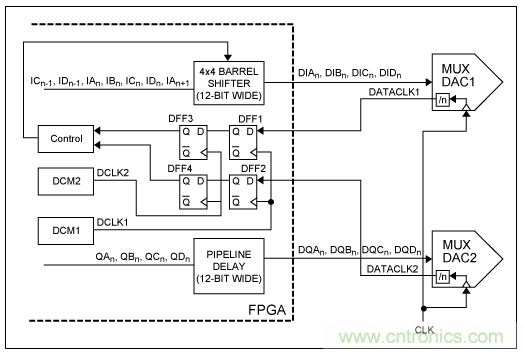

可以利用 Xilinx® FPGA 中先進的數(shù)字時鐘管理程序(DCM)來檢測兩個 MUX-DAC 的數(shù)據(jù)時鐘之間的相位差異(圖 6)。DCM1 生成一個與 DATACLK1 和 DATACLK2 相同頻率的時鐘。以時鐘周期的 1/256 為間距對 DCLK1 的延遲進行動態(tài)調(diào)整。觸發(fā)器 DFF1 和 DFF2 在每個時鐘周期對 DATACLK1 和 DATACLK2 進行一次采樣。如果 DFF1 在 DATACLK1 為低時采樣 DATACLK1,DFF1 會輸出固定的“0”。如果 DFF1 在 DATACLK1 為高時采樣 DATACLK1,DFF1 會輸出固定的“1”。所以 DFF3 和 DFF4 可在任意時鐘相位定時,與 DCLK1 的延遲設置無關。通過將 DCLK1 的延遲進行分級,使用 DCM1 的動態(tài)延遲調(diào)整功能以及讀取 DFF3 和 DFF4 的輸出,我們可以得到基于 DATACLK1 和 DATACLK2 上升沿的延遲設置。根據(jù)延遲設置,我們可以計算出為了保持 MUX-DAC1 和 MUX-DAC2 輸入數(shù)據(jù)的同相,MUX-DAC1 的輸入數(shù)據(jù)需要延遲的 DAC 時鐘周期數(shù)。FPGA 中 4 x 4 桶形移位器的實現(xiàn)可使數(shù)據(jù)等待時間以一個 DAC 時鐘周期為增量進行改變(參見圖 6)。

MAX19692 有四個并行數(shù)據(jù)端口 A、B、C 和 D。輸入 DAC 的數(shù)據(jù)序列是 An、Bn、 Cn、Dn、An+1、Bn+1、Cn+1、Dn+1、An+2 等。12 位 4 x 4 柱形移位器(圖 6)允許輸入 MUX-DAC1 的數(shù)據(jù)延遲 -1、0、1 或 2 個 CLK 周期。因此可以進行數(shù)據(jù)等待時間的調(diào)整直到兩個 DAC 的輸出數(shù)據(jù)同相。這樣的話,兩個 DAC 的數(shù)據(jù)時鐘可能相距幾個整數(shù)時鐘(CLK)周期且不再改變。由于 DAC 的建立和保持時間以數(shù)據(jù)時鐘為基準,所以兩個 DAC 的數(shù)據(jù)時序必須不同??梢酝ㄟ^驅(qū)動 DAC 的 FPGA 中的多個 DCM 來實現(xiàn)。

圖 6. 利用 FPGA 中桶形移位器的實現(xiàn)完成 MUX-DAC 的同步

每個 DAC 使用一個 PLL 實現(xiàn) DAC 同步

如果 DAC 使用鎖相環(huán)(PLL)合成器來定時,那么同步兩個 DAC 的方法就是每個 DAC 使用單獨的 PLL (圖 7)。DAC1 和 DAC2 的 LVDS 數(shù)據(jù)時鐘輸出相位與參考時鐘相比較。這樣的話,DAC 的內(nèi)部時鐘分頻器在時鐘生成 PLL 中作為反饋分頻器使用。

圖 7. 每個 DAC 使用一個 PLL 實現(xiàn) MUX-DAC 同步

這種方法中,兩個 DAC 的建立和保持時間相匹配。但是這種方法有兩個缺點,兩個 PLL 會帶來額外的成本且 PLL 的相位噪聲極限可能會造成性能極限。

結(jié)論

MAX19692 為 2.3Gsps、12 位、可工作于多個奈奎斯特頻帶內(nèi)的 DAC,具有集成的 4:1 輸入數(shù)據(jù)多路復用器,是 I/Q 應用中的理想器件。當 I/Q 應用中 MAX19692 的使用被強調(diào)時,所討論的方案同樣適用于其它 DAC 和應用,比如在多于兩個通道應用中使用的 MAX5858A。

免責聲明:本文為轉(zhuǎn)載文章,轉(zhuǎn)載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請電話或者郵箱聯(lián)系小編進行侵刪。