【導(dǎo)讀】在學(xué)習(xí)電路設(shè)計(jì)的時(shí)候,不知道你是否有這樣的困擾:明明自己學(xué)了很多硬件電路理論,也做過(guò)了一些基礎(chǔ)操作實(shí)踐,但還是無(wú)法設(shè)計(jì)出自己理想的電路。歸根結(jié)底,我們?nèi)鄙俚氖怯布娐吩O(shè)計(jì)的思路以及項(xiàng)目實(shí)戰(zhàn)經(jīng)驗(yàn)。

設(shè)計(jì)一款硬件電路,要熟悉元器件的基礎(chǔ)理論,比如元器件原理、選型及使用,學(xué)會(huì)繪制原理圖,并通過(guò)軟件完成PCB設(shè)計(jì),熟練掌握工具的技巧使用,學(xué)會(huì)如何優(yōu)化及調(diào)試電路等。要如何完整地設(shè)計(jì)一套硬件電路設(shè)計(jì),下面為大家分享我的幾點(diǎn)個(gè)人經(jīng)驗(yàn):

1)總體思路

設(shè)計(jì)硬件電路,大的框架和架構(gòu)要搞清楚,但要做到這一點(diǎn)還真不容易。有些大框架也許自己的老板、老師已經(jīng)想好,自己只是把思路具體實(shí)現(xiàn);但也有些要自己設(shè)計(jì)框架的,那就要搞清楚要實(shí)現(xiàn)什么功能,然后找找有否能實(shí)現(xiàn)同樣或相似功能的參考電路板(要懂得盡量利用他人的成果,越是有經(jīng)驗(yàn)的工程師越會(huì)懂得借鑒他人的成果)。

2)理解電路

如果你找到了的參考設(shè)計(jì),那么恭喜你,你可以節(jié)約很多時(shí)間了(包括前期設(shè)計(jì)和后期調(diào)試)。馬上就copy?NO,還是先看懂理解了再說(shuō),一方面能提高我們的電路理解能力,而且能避免設(shè)計(jì)中的錯(cuò)誤。

3)找到參考設(shè)計(jì)

在開(kāi)始做硬件設(shè)計(jì)前,根據(jù)自己的項(xiàng)目需求,可以去找能夠滿(mǎn)足硬件功能設(shè)計(jì)的,有很多相關(guān)的參考設(shè)計(jì)。沒(méi)有找到?也沒(méi)關(guān)系,先確定大IC芯片,找datasheet,看其關(guān)鍵參數(shù)是否符合自己的要求,哪些才是自己需要的關(guān)鍵參數(shù),以及能否看懂這些關(guān)鍵參數(shù),都是硬件工程師的能力的體現(xiàn),這也需要長(zhǎng)期地慢慢地積累。這期間,要善于提問(wèn),因?yàn)樽约翰欢臇|西,別人往往一句話(huà)就能點(diǎn)醒你,尤其是硬件設(shè)計(jì)。

4)硬件電路設(shè)計(jì)的三個(gè)部分:原理圖、PCB和物料清單(BOM)表

原理圖設(shè)計(jì),其實(shí)就是將前面的思路轉(zhuǎn)化為電路原理圖,它很像我們教科書(shū)上的電路圖。pcb涉及到實(shí)際的電路板,它根據(jù)原理圖轉(zhuǎn)化而來(lái)的網(wǎng)表(網(wǎng)表是溝通原理圖和pcb之間的橋梁),而將具體的元器件的封裝放置(布局)在電路板上,然后根據(jù)飛線(xiàn)(也叫預(yù)拉線(xiàn))連接其電信號(hào)(布線(xiàn))。完成了pcb布局布線(xiàn)后,要用到哪些元器件應(yīng)該有所歸納,所以我們將用到BOM表。

5)選擇PCB設(shè)計(jì)工具

Protel,也就是Altium(現(xiàn)在入門(mén)的童鞋大多用AD)容易上手,網(wǎng)上的學(xué)習(xí)教程資料也很全面,在國(guó)內(nèi)也比較流行,應(yīng)付一般的工作已經(jīng)足夠,適合初入門(mén)的設(shè)計(jì)者使用。

硬件電路設(shè)計(jì)的大環(huán)節(jié)必不可少,主要都要經(jīng)過(guò)以下這幾個(gè)流程:

1)原理圖設(shè)計(jì)

2)PCB設(shè)計(jì)

3)制作BOM表

現(xiàn)在再談一下具體的設(shè)計(jì)步驟

原理圖建立+網(wǎng)表生成

1. 原理圖庫(kù)建立。要將一個(gè)新元件擺放在原理圖上,我們必須得建立改元件的庫(kù)。庫(kù)中主要定義了該新元件的管腳定義及其屬性,并且以具體的圖形形式來(lái)代表(我們常常看到的是一個(gè)矩形(代表其IC BODY),周?chē)S多短線(xiàn)(代表IC管腳))。protel創(chuàng)建庫(kù)及其簡(jiǎn)單,而且因?yàn)橛玫娜硕?,許多元件都能找到現(xiàn)成的庫(kù),這一點(diǎn)對(duì)使用者極為方便。應(yīng)搞清楚ic body,ic pins,input pin,output pin,analog pin,digital pin,power pin等區(qū)別。

2. 有了充足的庫(kù)之后,就可以在原理圖上畫(huà)圖了,按照datasheet和系統(tǒng)設(shè)計(jì)的要求,通過(guò)wire把相關(guān)元件連接起來(lái)。在相關(guān)的地方添加line和text注釋。wire和line的區(qū)別在于,前者有電氣屬性,后者沒(méi)有。wire適用于連接相同網(wǎng)絡(luò),line適用于注釋圖形。這個(gè)時(shí)候,應(yīng)搞清一些基本概念,如:wire,line,bus,part,footprint,等等。

3. 做完這一步,我們就可以生成netlist了,這個(gè)netlist是原理圖與pcb之間的橋梁。原理圖是我們能認(rèn)知的形式,電腦要將其轉(zhuǎn)化為pcb,就必須將原理圖轉(zhuǎn)化它認(rèn)識(shí)的形式netlist,然后再處理、轉(zhuǎn)化為pcb。

4. 得到netlist,馬上畫(huà)pcb?別急,先做ERC先。ERC是電氣規(guī)則檢查的縮寫(xiě)。它能對(duì)一些原理圖基本的設(shè)計(jì)錯(cuò)誤進(jìn)行排查,如多個(gè)output接在一起等問(wèn)題。(但是一定要仔細(xì)檢查自己的原理圖,不能過(guò)分依賴(lài)工具,畢竟工具并不能明白你的系統(tǒng),它只是純粹地根據(jù)一些基本規(guī)則排查。)

5. 從netlist得到了pcb,一堆密密麻麻的元件,和數(shù)不清的飛線(xiàn)是不是讓你嚇了一跳?呵呵,別急還得慢慢來(lái)。

6. 確定板框大小。在keepout區(qū)(或mechanic區(qū))畫(huà)個(gè)板框,這將限制了你布線(xiàn)的區(qū)域。需要根據(jù)需求好考慮板長(zhǎng),板寬(有時(shí),還得考慮板厚)。當(dāng)然了,疊層也得考慮好。(疊層的意思就是,板層有幾層,怎么應(yīng)用,比如板總共4層,頂層走信號(hào),中間第一層鋪電源,中間第二層鋪地,底層走信號(hào))。

PCB布局布線(xiàn)

先解釋一下前面的術(shù)語(yǔ)。post-command,例如我們要拷貝一個(gè)object(元件),我們要先選中這個(gè)object,然后按ctrl+C,然后按ctrl+V(copy命令發(fā)生在選中object之后)。這種操作windows和protel都采用的這種方式。但是concept就是另外一種方式,我們叫做pre-command。同樣我們要拷貝一個(gè)東西,先按ctrl+C,然后再選中object,再在外面單擊(copy命令發(fā)生在選中object之前)。

1. 確定完板框之后,就該元件布局(擺放)了,布局這步極為關(guān)鍵。它往往決定了后期布線(xiàn)的難易。哪些元器件該擺正面,哪些元件該擺背面,都要有所考量。但是這些都是一個(gè)仁者見(jiàn)仁,智者見(jiàn)智的問(wèn)題;從不同角度考慮擺放位置都可以不一樣。其實(shí)自己畫(huà)了原理圖,明白所有元件功能,自然對(duì)元件擺放有清楚的認(rèn)識(shí)(如果讓一個(gè)不是畫(huà)原理圖的人來(lái)擺放元件,其結(jié)果往往會(huì)讓你大吃一驚。對(duì)于初入門(mén)的,注意模擬元件,數(shù)字元件的隔離,以及機(jī)械位置的擺放,同時(shí)注意電源的拓?fù)渚涂梢粤恕?/div>

2. 接下來(lái)就是布線(xiàn)。這與布局往往是互動(dòng)的。有經(jīng)驗(yàn)的人往往在開(kāi)始就能看出哪些地方能布線(xiàn)成功。如果有些地方難以布線(xiàn)還需要改動(dòng)布局。對(duì)于fpga設(shè)計(jì)來(lái)說(shuō)往往還要改動(dòng)原理圖來(lái)使布線(xiàn)更加順暢。布線(xiàn)和布局問(wèn)題涉及的因素很多,對(duì)于高速數(shù)字部分,因?yàn)闋砍兜叫盘?hào)完整性問(wèn)題而變得復(fù)雜,但往往這些問(wèn)題又是難以定量或即使定量也難以計(jì)算的。所以,在信號(hào)頻率不是很高的情況下,應(yīng)以布通為第一原則。

3. OK了?別急,用DRC檢查檢查先,這是一定要檢查的。DRC對(duì)于布線(xiàn)完成覆蓋率以及規(guī)則違反的地方都會(huì)有所標(biāo)注,按照這個(gè)再一一的排查,修正。

4. 有些pcb還要加上敷銅(可能會(huì)導(dǎo)致成本增加),將出線(xiàn)部分做成淚滴(工廠也許會(huì)幫你加)。最后的pcb文件轉(zhuǎn)成gerber文件就可交付pcb生產(chǎn)了。(有些直接給pcb也成,工廠會(huì)幫你轉(zhuǎn)gerber)。

5. 要裝配pcb,準(zhǔn)備bom表吧,一般能直接從原理圖中導(dǎo)出。但是需要注意的是,原理圖中哪些部分元件該上,哪些部分元件不該上,要做到心理有數(shù)。對(duì)于小批量或研究板而言,用excel自己管理倒也方便(大公司往往要專(zhuān)業(yè)軟件來(lái)管理)。而對(duì)于新手而言,第一個(gè)版本,不建議直接交給裝配工廠或焊接工廠將bom的料全部焊上,這樣不便于排查問(wèn)題。最好的方法就是,根據(jù)bom表自己準(zhǔn)備好元件。等到板來(lái)了之后,一步步上元件、調(diào)試。

電路板調(diào)試

1. 拿到板第一步做什么,不要急急忙忙供電看功能,硬件調(diào)試不可能一步調(diào)試完成的。先拿萬(wàn)用表看看關(guān)鍵網(wǎng)絡(luò)是否有不正常,主要是看電源與地之間有否短路(盡管生產(chǎn)廠商已經(jīng)幫你做過(guò)測(cè)試,這一步還是要自己親自看看,有時(shí)候看起來(lái)某些步驟挺繁瑣,但是可以節(jié)約你后面不少時(shí)間!),其實(shí)短路與否不光pcb有關(guān),在生產(chǎn)制作的任何一個(gè)環(huán)節(jié)可能導(dǎo)致這個(gè)問(wèn)題,IO短路一般不會(huì)造成災(zāi)難性的后果,但是電源短路就......

2. 電源網(wǎng)絡(luò)沒(méi)短路?那么好,那就看看電源輸出是否是自己理想的值,對(duì)于初學(xué)者,調(diào)試的時(shí)候最好IC一件件芯片上,第一個(gè)要上的就是電源芯片。

3. 電源網(wǎng)絡(luò)短路了?這個(gè)比較麻煩,不過(guò)要仔細(xì)看看自己原理圖是否有可能這樣的情況,同時(shí)結(jié)合割線(xiàn)的方法一步步排查倒底是什么地方短路了,是pcb的問(wèn)題(一般比較爛的pcb廠就可能出現(xiàn)這種情況),還是裝配的問(wèn)題,還是自己設(shè)計(jì)的問(wèn)題。關(guān)于檢查短路還有一些技巧,這在今后登出......

4. 電源芯片沒(méi)有輸出?檢查檢查你的電源芯片輸入是否正常吧,還需要檢查的地方有使能信號(hào),分壓電阻,反饋網(wǎng)絡(luò)......

5. 電源芯片輸出值不在預(yù)料范圍?如果超過(guò)很離譜,比如到了10%,那么看看分壓電阻先,這兩個(gè)分壓電阻一般要用1%的精度,這個(gè)你做到了沒(méi)有,同時(shí)看看反饋網(wǎng)絡(luò)吧,這也會(huì)影響你的輸出電源的范圍。

6. 電源輸出正常了,別高興,如果有條件的話(huà),拿示波器看看吧,看看電源的輸出跳變是否正常。也就是抓取開(kāi)電的瞬間,看看電源從無(wú)到有的情況(至于為什么要看著個(gè),嘿嘿......專(zhuān)業(yè)人士還是要看的~)

電源設(shè)計(jì)

無(wú)疑電源設(shè)計(jì)是整個(gè)電路板最重要的一環(huán)。電源不穩(wěn)定,其他啥都別談。我想不用balabala述說(shuō)它究竟有多么重要了。

在電源設(shè)計(jì)我們用得最多的場(chǎng)合是,從一個(gè)穩(wěn)定的“高”電壓得到一個(gè)穩(wěn)定的“低”電壓。這也就是經(jīng)常說(shuō)的DC/DC,其中用得最多的電源穩(wěn)壓芯片有兩種,一種叫LDO(低壓差線(xiàn)性穩(wěn)壓器,我們后面說(shuō)的線(xiàn)性穩(wěn)壓電源,也是指它),另一種叫PWM(脈寬調(diào)制開(kāi)關(guān)電源,我們?cè)诒疚囊卜Q(chēng)它開(kāi)關(guān)電源)。我們常常聽(tīng)到PWM的效率高,但是LDO的響應(yīng)快,這是為什么呢?別著急,先讓我們看看它們的原理。

下面會(huì)涉及一些理論知識(shí),但是依然非常淺顯易懂,如果你不懂,嘿嘿,得檢查一下自己的基礎(chǔ)了。

一、線(xiàn)性穩(wěn)壓電源的工作原理

如圖是線(xiàn)性穩(wěn)壓電源內(nèi)部結(jié)構(gòu)的簡(jiǎn)單示意圖。我們的目的是從高電壓Vs得到低電壓Vo。在圖中,Vo經(jīng)過(guò)兩個(gè)分壓電阻分壓得到V+,V+被送入放大器(我們把這個(gè)放大器叫做誤差放大器)的正端,而放大器的負(fù)端Vref是電源內(nèi)部的參考電平(這個(gè)參考電平是恒定的)。放大器的輸出Va連接到MOSFET的柵極來(lái)控制MOSFET的阻抗。Va變大時(shí),MOSFET的阻抗變大;Va變小時(shí),MOSFET的阻抗變小。MOSFET上的壓降將是Vs-Vo。

現(xiàn)在我們來(lái)看Vo是怎么穩(wěn)定的,假設(shè)Vo變小,那么V+將變小,放大器的輸出Va也將變小,這將導(dǎo)致MOSFET的阻抗變小,這樣經(jīng)過(guò)同樣的電流,MOSFET的壓差將變小,于是將Vo上抬來(lái)抑制Vo的變小。同理,Vo變大,V+變大,Va變大,MOSFET的阻抗變大,經(jīng)過(guò)同樣的電流,MOSFET的壓差變大,于是抑制Vo變大。

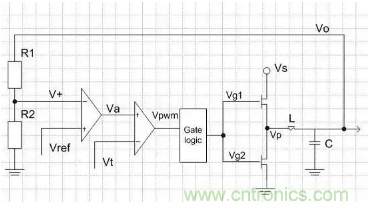

二、開(kāi)關(guān)電源的工作原理

如上圖,為了從高電壓Vs得到Vo,開(kāi)關(guān)電源采用了用一定占空比的方波Vg1,Vg2推動(dòng)上下MOS管,Vg1和Vg2是反相的,Vg1為高,Vg2為低;上MOS管打開(kāi)時(shí),下MOS管關(guān)閉;下MOS管打開(kāi)時(shí),上MOS管關(guān)閉。由此在L左端形成了一定占空比的方波電壓,電感L和電容C我們可以看作是低通濾波器,因此方波電壓經(jīng)過(guò)濾波后就得到了濾波后的穩(wěn)定電壓Vo。Vo經(jīng)過(guò)R1、R2分壓后送入第一個(gè)放大器(誤差放大器)的負(fù)端V+,誤差放大器的輸出Va做為第二個(gè)放大器(PWM放大器)的正端,PWM放大器的輸出Vpwm是一個(gè)有一定占空比的方波,經(jīng)過(guò)門(mén)邏輯電路處理得到兩個(gè)反相的方波Vg1、Vg2來(lái)控制MOSFET的開(kāi)關(guān)。

誤差放大器的正端Vref是一恒定的電壓,而PWM放大器的負(fù)端Vt是一個(gè)三角波信號(hào),一旦Va比三角波大時(shí),Vpwm為高;Va比三角波小時(shí),Vpwm為低,因此Va與三角波的關(guān)系,決定了方波信號(hào)Vpwm的占空比;Va高,占空比就低,Va低,占空比就高。經(jīng)過(guò)處理,Vg1與Vpwm同相,Vg2與Vpwm反相;最終L左端的方波電壓Vp與Vg1相同。如下圖

當(dāng)Vo上升時(shí),V+將上升,Va下降,Vpwm占空比下降,經(jīng)過(guò)們邏輯之后,Vg1的占空比下降,Vg2的占空比上升,Vp占空比下降,這又導(dǎo)致Vo降低,于是Vo的上升將被抑制。反之亦然。

三、線(xiàn)性穩(wěn)壓電源和開(kāi)關(guān)電源的比較

懂得了線(xiàn)性穩(wěn)壓電源和開(kāi)關(guān)電源的工作原理之后,我們就可以明白為什么線(xiàn)性穩(wěn)壓電源有較小的噪聲,較快的瞬態(tài)響應(yīng),但是效率差;而開(kāi)關(guān)電源噪聲較大,瞬態(tài)響應(yīng)較慢,但效率高了。

線(xiàn)性穩(wěn)壓電源內(nèi)部結(jié)構(gòu)簡(jiǎn)單,反饋環(huán)路短,因此噪聲小,而且瞬態(tài)響應(yīng)快(當(dāng)輸出電壓變化時(shí),補(bǔ)償快)。但是因?yàn)檩斎牒洼敵龅膲翰钊柯湓诹薓OSFET上,所以它的效率低。因此,線(xiàn)性穩(wěn)壓一般用在小電流,對(duì)電壓精度要求高的應(yīng)用上。

而開(kāi)關(guān)電源,內(nèi)部結(jié)構(gòu)復(fù)雜,影響輸出電壓噪聲性能的因數(shù)很多,且其反饋環(huán)路長(zhǎng),因此其噪聲性能低于線(xiàn)性穩(wěn)壓電源,且瞬態(tài)響應(yīng)慢。但是根據(jù)開(kāi)關(guān)電源的結(jié)構(gòu),MOSFET處于完全開(kāi)和完全關(guān)兩種狀態(tài),除了驅(qū)動(dòng)MOSFET,和MOSFET自己內(nèi)阻消耗的能量之外,其他能量被全部用在了輸出(理論上L、C是不耗能量的,盡管實(shí)際并非如此,但這些消耗的能量很小)。

總而言之,要學(xué)好硬件電路設(shè)計(jì),首先要弄清楚項(xiàng)目需求,根據(jù)功能設(shè)計(jì)硬件框架,結(jié)合參考設(shè)計(jì),多借鑒別人的設(shè)計(jì)成果,復(fù)用到自己的硬件項(xiàng)目上面來(lái)。