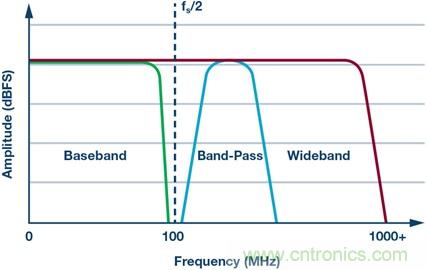

【導(dǎo)讀】開始一個新設(shè)計時,需要決定的首要參數(shù)就是帶寬。帶寬為設(shè)計指明方向,引導(dǎo)設(shè)計人員開辟通往成功之路。本質(zhì)上有三類前端可供選擇:基帶型、帶通或超奈奎斯特型(有時也稱為窄帶或子采樣型——基本上不會用到第1奈奎斯特區(qū))以及寬帶型,如圖1所示。前端的選用取決于具體應(yīng)用。

圖1. 基帶、帶通與寬帶,F(xiàn)SAMPLE = 200 MSPS。

基帶設(shè)計要求的帶寬是從直流(或低kHz/MHz區(qū))到轉(zhuǎn)換器的奈奎斯特頻率。用相對帶寬表示的話,這意味著大約100 MHz或以下,假定采樣速率為200 MSPS。這類設(shè)計可以采用放大器或變壓器/巴倫。

帶通設(shè)計意味著在高中頻時只會使用轉(zhuǎn)換器帶寬的一小部分(即小于奈奎斯特頻率)。例如,還是假定采樣速率為200 MSPS,可能只需要20-60MHz帶寬,以170 MHz為中心。不過,隨著新一代GSPS轉(zhuǎn)換器類型產(chǎn)品的發(fā)布,市場呈現(xiàn)出向更高中頻發(fā)展的趨勢。因此,上述示例中的數(shù)值可能會多填充一個0。本質(zhì)上講,設(shè)計人員只需利用轉(zhuǎn)換器帶寬的一小部分就能完成工作。這種設(shè)計通常使用變壓器或巴倫。不過,如果較高頻率下的動態(tài)性能足夠并且需要增益,也可以使用放大器。

寬帶設(shè)計通常指需要全部帶寬的設(shè)計。轉(zhuǎn)換器能夠提供多少帶寬,用戶就會使用多少帶寬——供大于求!在三種設(shè)計中,這種設(shè)計的帶寬最寬,因而是最具挑戰(zhàn)性的前端設(shè)計。如果設(shè)計要求整個通帶的平坦度為0.1dB,則更具挑戰(zhàn)性。這類應(yīng)用的帶寬范圍為直流或低kHz/MHz區(qū)至+GHz區(qū)。此類設(shè)計常常采用寬帶巴倫耦合到轉(zhuǎn)換器。

關(guān)于帶寬的說明

術(shù)語"帶寬"在工程領(lǐng)域中遭到濫用,根據(jù)應(yīng)用的不同,帶寬的含義在不同設(shè)計人員看來可能完全不同。在本文中,轉(zhuǎn)換器的全功率帶寬與轉(zhuǎn)換器的可用帶寬或采樣帶寬是不同的。全功率帶寬是轉(zhuǎn)換器用于精確捕獲信號以及內(nèi)置前端正確建立所需要的帶寬。在多數(shù)情況下,轉(zhuǎn)換器的采樣帶寬目標(biāo)是在大約兩個奈奎斯特區(qū)撥入。轉(zhuǎn)換器通常也是以這種方式在其交流頻率規(guī)格范圍內(nèi)進(jìn)行表征。

設(shè)計人員在轉(zhuǎn)換器指定區(qū)域外選擇中頻并不是個明智的選擇,因?yàn)橄到y(tǒng)的交流性能結(jié)果會存在較大差異,盡管轉(zhuǎn)換器數(shù)據(jù)手冊中說明了額定分辨率和性能,或顯示的全功率帶寬遠(yuǎn)大于轉(zhuǎn)換器本身的采樣帶寬(可能是其兩倍)。設(shè)計應(yīng)圍繞采樣帶寬展開。所有設(shè)計都應(yīng)當(dāng)避免使用額定全功率帶寬的某一或全部最高頻率部分,否則動態(tài)性能(SNR/SFDR)會下降。為了確定高速模數(shù)轉(zhuǎn)換器的采樣帶寬,請查閱數(shù)據(jù)手冊,或者咨詢應(yīng)用支持人員,因?yàn)橛袝r候采樣帶寬并未明確給出。通常,數(shù)據(jù)手冊會規(guī)定甚至列出轉(zhuǎn)換器采樣帶寬內(nèi)經(jīng)過生產(chǎn)測試、能夠保證額定性能的頻率。然而,需要對行業(yè)中的這些帶寬術(shù)語做出更好的說明和定義。

了解轉(zhuǎn)換器帶寬和精度

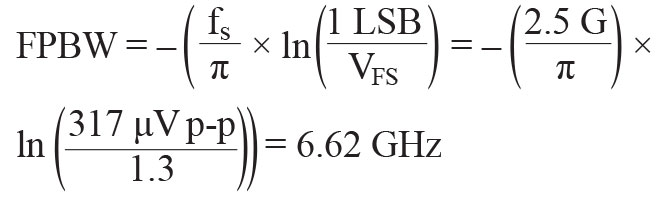

所有的ADC都存在建立時間不精確的問題。記住,轉(zhuǎn)換器的內(nèi)部前端必須具有足夠的帶寬(BW),才能精確地對信號進(jìn)行采樣。否則,累積誤差將大于上文所述的結(jié)果。一般而言,一個ADC的內(nèi)部前端必須在半個采樣時鐘周期內(nèi)建立(0.5/fs,其中fs =采樣頻率),這樣才能提供對內(nèi)模擬信號捕捉的精確表達(dá)。因此,對于一個12位ADC(采樣速率為2.5 GSPS,滿量程輸入范圍(VFS)為1.3 V p-p)來說,全功率帶寬(FPBW)可通過下列瞬態(tài)公式推導(dǎo):

求解 t:

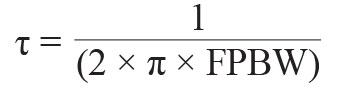

代入 τ = 1/(2 × π × FPBW),一個時間常數(shù),求解FPBW:

令 t = 0.5/fs。這是樣本建立所需的時間,其中采樣周期為1/fs:

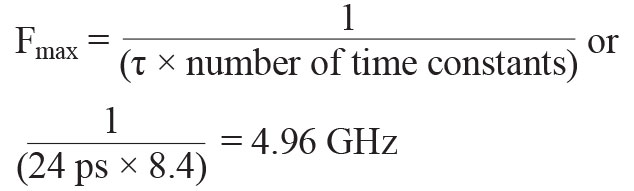

這樣會使ADC內(nèi)部前端FPBW所需的帶寬最小。轉(zhuǎn)換器內(nèi)部前端需要這一大小的帶寬,以建立至1 LSB以內(nèi)并正確采樣模擬信號。這將需要通過數(shù)個時間常數(shù)來滿足這類ADC的1 LSB精度要求,其中1個時間常數(shù)等于24 ps或:

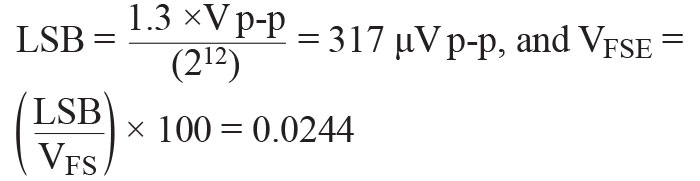

要了解ADC滿量程范圍內(nèi)達(dá)到LSB大小要求所需的時間常數(shù)數(shù)量,就需要找出滿量程誤差%或VFSE?;? LSB = VFS/(2N),其中N =位數(shù);或

表1列出了不同分辨率的轉(zhuǎn)換器與各自的位數(shù)、LSB大小和VFSE的關(guān)系細(xì)分表。

表1. 轉(zhuǎn)換器分辨率明細(xì)表

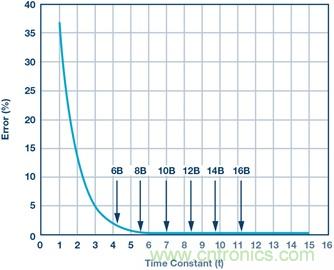

通過描繪歐拉數(shù)或eτ,可以繪出一條曲線,以便每次通過時間常數(shù)都能方便地看出相對誤差。從圖2可見,12位ADC樣本建立至大約1 LSB以內(nèi)需時8.4個時間常數(shù)。

圖2. 轉(zhuǎn)換器采樣精度與時間常數(shù)數(shù)量:ADC精確建立至½ LSB以內(nèi)所需要的時間常數(shù)數(shù)量。

設(shè)計人員可通過這種分析來估算轉(zhuǎn)換器能處理的最大模擬輸入頻率或采樣帶寬,并依舊建立至1 LSB誤差以內(nèi)。超出這個范圍,則ADC無法精確表示信號。因此:

記住,這里表示的是最佳情形,并假定采用單極點(diǎn)ADC前端。并非所有現(xiàn)實(shí)中的轉(zhuǎn)換器都以這種方式工作,但這是一個很好的開端。

例如,上文描述的模型最高可適用至12位。但針對14或16位以及更高位則需要采用二階模型,因?yàn)榧?xì)微的影響可使建立時間擴(kuò)展至預(yù)測的一階模型以外。

本文轉(zhuǎn)載自亞德諾半導(dǎo)體。

推薦閱讀: